# LEADING THE EVOLUTION OF COMPUTE: QUANTUM COMPUTING

Anne Matsuura, Ph.D. Director, Quantum Applications & Architecture Intel Labs

Teratec HPC Forum June 20, 2018

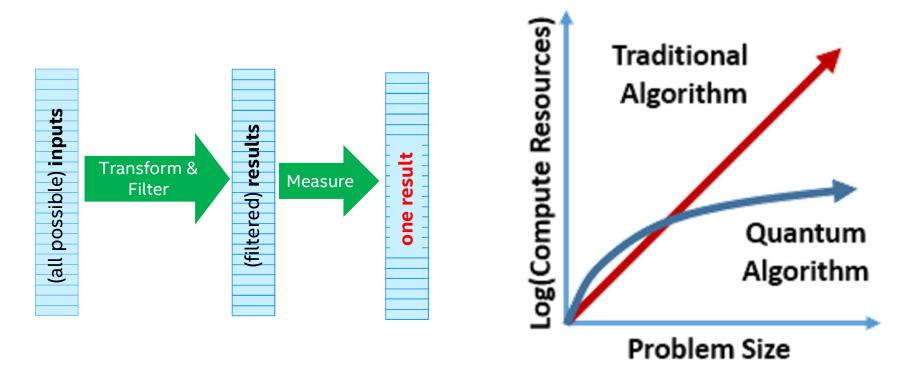

### The promise of quantum computing

Exponential speedup  $\leftarrow \rightarrow$  surpassing the limits of scaling

(intel)

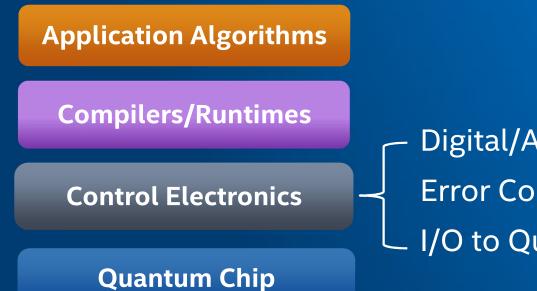

**Application Algorithms**

**Compilers/Runtimes**

**Control Electronics**

**Quantum Chip**

Challenges to be addresses at each level

Application Algorithms

**Compilers/Runtimes**

**Control Electronics**

**Quantum Chip**

**Compelling Applications**

- **Resilient Algorithms**

- Real Workloads for Early Systems

## **Applications Space: HPC**

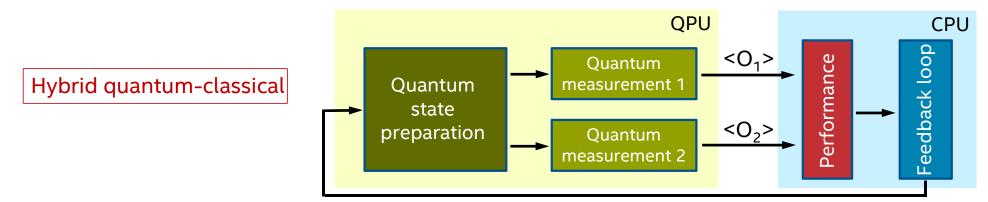

Quantum co-processor: augmenting, not replacing, traditional HPC systems

### ~50+ Qubits: Proof of concept

- Computational power exceeds

supercomputers

- Learning test bed for quantum "system"

### ~1000+ Qubits: Small problems

- Limited error correction

- Chemistry, materials design

- Optimization

### ~1M+ Qubits: Commercial scale

- Fault tolerant operation

- Cryptography

- Machine Learning

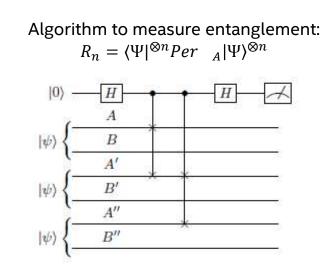

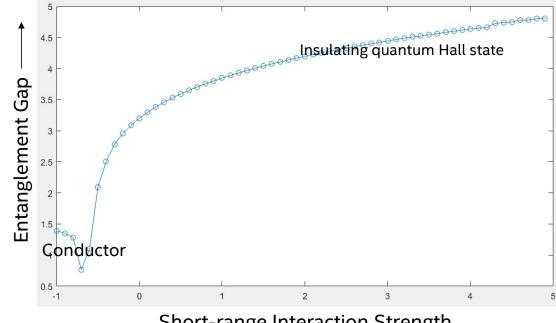

Quantifying entanglement provides a measurement of correlations between electrons which is useful for understanding the electronic properties of the material.

For example, in determining whether simulated material is a metal or an insulator.

Collaboration: Damian Steiger, Matthias Troyer (ETH Zurich), Chris Monroe (U of MD)

Short-range Interaction Strength

**6**<sub>6</sub>

(inte

## **Resilient Algorithms**

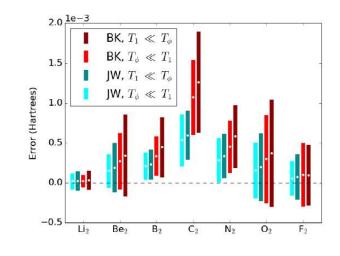

### Quantum Chemistry and Noise study:

- Comparing two variants of the VQE algorithm to approximate lowest energy of molecules

- Surprisingly, version requiring more quantum operations is more resilient to noise

Collaboration: Alan Aspuru-Guzik, Harvard, Jarrod McClean, LBL

(intel

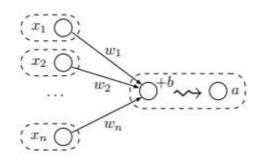

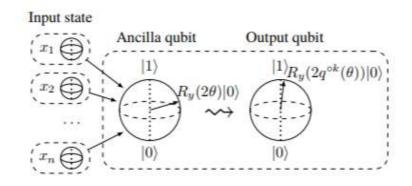

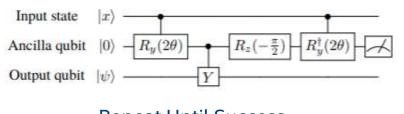

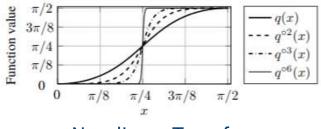

## **Machine Learning**

**Classical Neuron**

#### Quantum Neuron

Repeat Until Success circuit

Collaboration: Yudong Cao and Alán Aspuru-Guzik, Harvard University

Non-linear Transfer Function

## **Qubit Simulation – Intel Quantum Simulator**

#### Universal: single and two-qubit controlled gates

#### 31.85 1.18 GE/s 13.27 Time Per Single Qubit Gate (s) 5.53 2.30 **General Single Qubit Gate on** 0.96 **NERSC Edison Supercomputer** 42 GB/s -2,048 nodes / 42 qubits 0.40 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 **Qubit Position** www.nersc.gov/systems/edison-cray-xc30/

#### High Perf QuBit Simulation

#### **Open Source Release**

External Collaboration: Alan Aspuru-Guzik (Harvard), Matthias Troyer (ETH Zürich)

9<sub>9</sub>

**Compilers/Runtimes**

**Control Electronics**

**Quantum Chip**

Optimization

Mapping & Scheduling

Fault tolerant operations

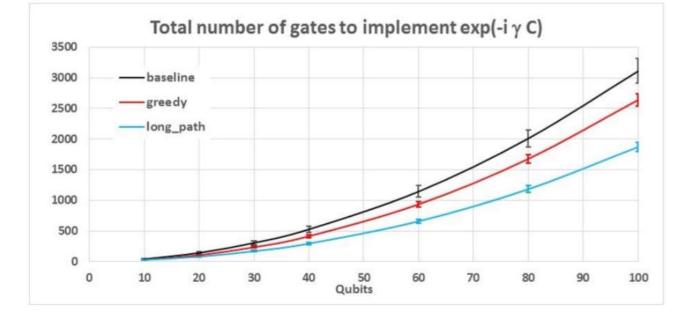

## Gate scheduling for quantum algorithms

Mapping and scheduling under constraints:

- Logical dependency

- Exclusive activation

- Physical connectivity

Scheduling Quantum Approximate Optimization Algorithm for hardware with linear connectivity: three strategies of increasing sophistication

(intel)

### Intel Labs:

- Algorithms

- System Architecture

- Control Electronics

### **TMG Components Research**

#### Patterning

Atomic Layer Control

Packaging

24nm Pitch Lines

#### Metal Gate / High k on 300mm Silicon Wafer

Assembly and Packaging Research

### QuTech's Expertise in qubit operation and control

### **Combining Intel capabilities with Delft expertise**

Digital/Analog Control

Error Correction

I/O to Qubit plane

14

(intel

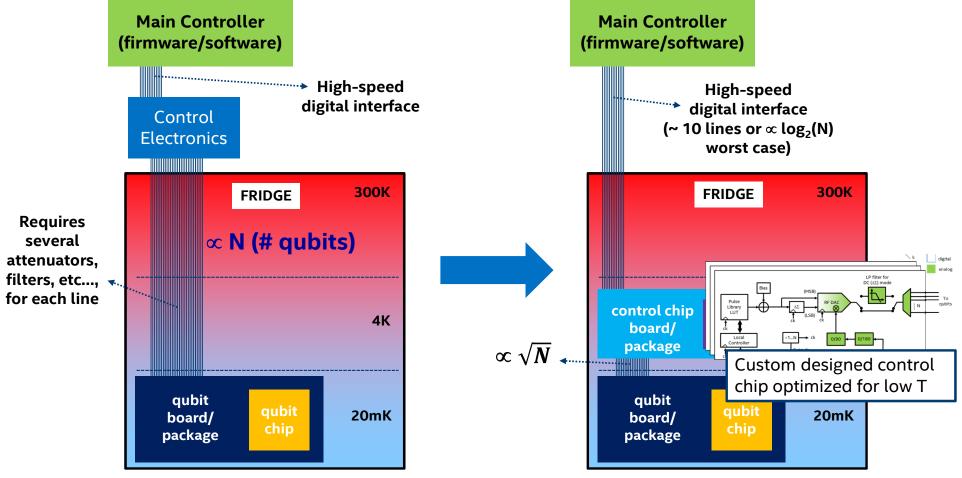

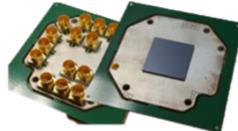

## Scaling I/O to the Qubit Plane

Processor

- 10<sup>9</sup> transistors

- 10<sup>3</sup> pins

### 3D NAND Memory

- 10<sup>12</sup> bytes

- 10<sup>2</sup> pins

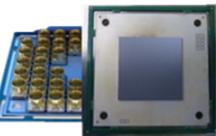

### 49-Qubit Transmon Array

- 49 qubits

- 108 pins

**Application Algorithms**

**Compilers/Runtimes**

**Control Electronics**

**Quantum Chip**

Qubit Device Design & Fabrication

Assembly & Packaging

Topology & Connectivity

## **Building Better Qubits**

### **Superconducting Qubits**

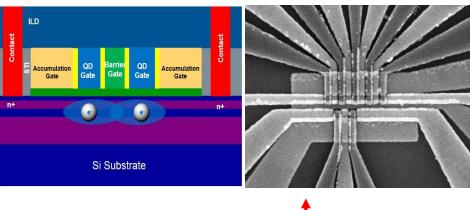

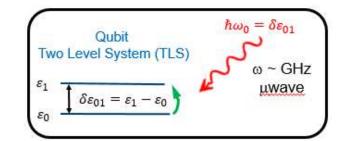

### **Spin Qubits in Silicon**

Very high quality microwave circuit

Single electron transistors, where qubit is spin state

(intel)

## **Superconducting Qubit Progress**

6 Qubits

Resonator

Starmon Geometry with up to 30us T1

7 Qubit Array

### Shared Feedlines

17 Qubit Array

Tangle Lake

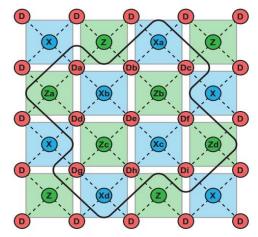

Surface Code Topology

(intel)

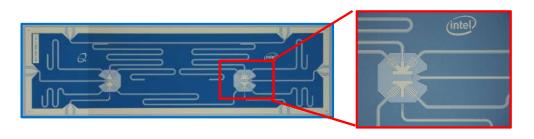

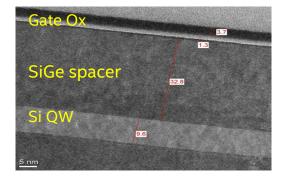

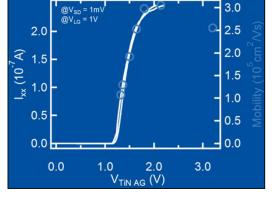

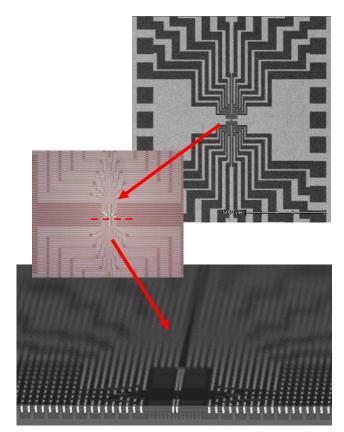

## Spin Qubits In Silicon

Characterizing LAB devices

First 300mm isotopically pure silicon and world class mobility

QD array devices almost ready with FAB quality Si

### **Application Algorithms**

**Compilers/Runtimes**

**Control Electronics**

**Quantum Chip**

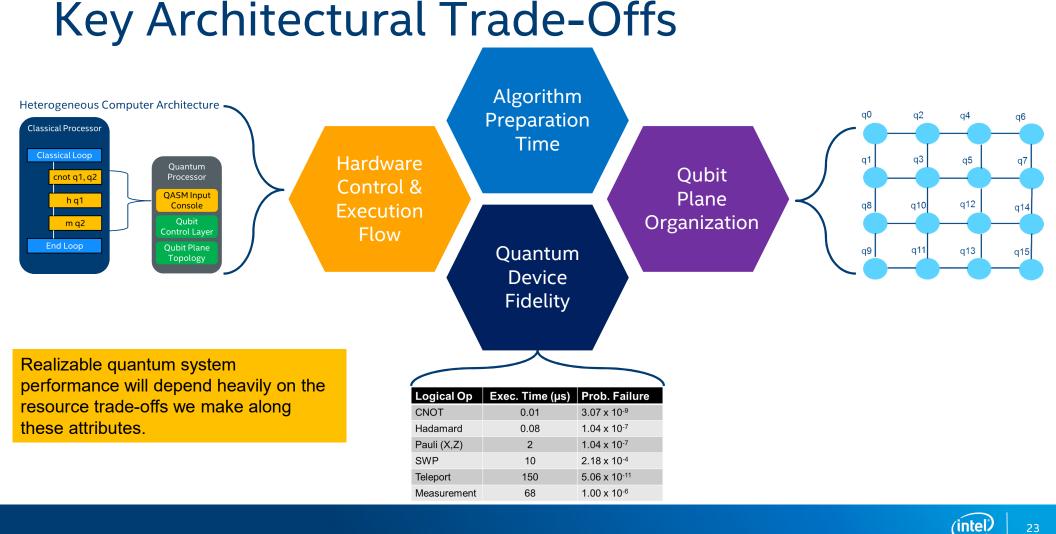

System Metrics Trade-offs & Constraints Co-design for scaling

## **Moving to System Level Metrics**

### **Device-level metrics**

- Physical qubit count

- Decoherence time T<sub>1</sub>, T<sub>2</sub>

### System-level metrics

- Gate operation time

- Fidelity

- Logical qubit count

- Effective parallelization

- Utilization

...

HW-SW co-design requires system metrics that impact real application performance

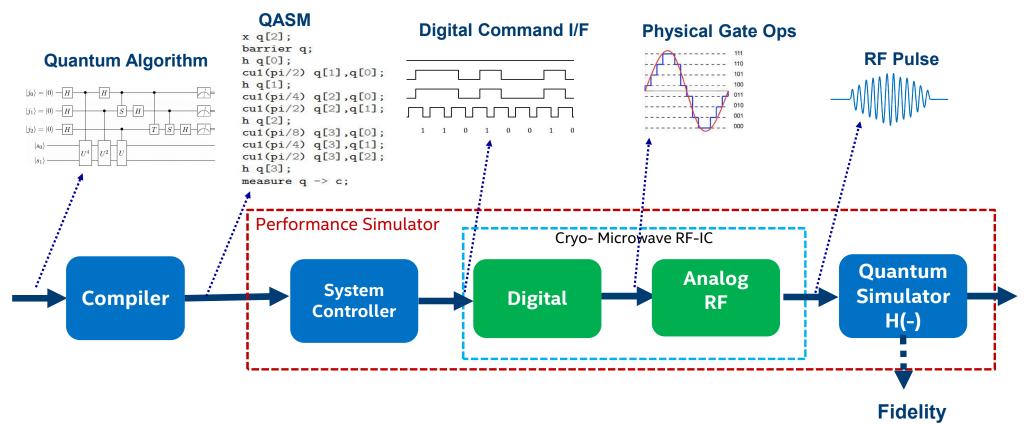

## System-level performance simulation

(intel) 22

## Conclusions

- The potential of quantum computing is generating tremendous excitement

- We're leveraging Intel's expertise in process and architecture to move faster

- A commercial system is ~10 Years Away

## Legal Information

This presentation contains the general insights and opinions of Intel Corporation ("Intel"). The information in this presentation is provided for information only and is not to be relied upon for any other purpose than educational. Statements in this document that refer to Intel's plans and expectations for the quarter, the year, and the future, are forward-looking statements that involve a number of risks and uncertainties. A detailed discussion of the factors that could affect Intel's results and plans is included in Intel's SEC filings, including the annual report on Form 10-K.

Any forecasts of goods and services needed for Intel's operations are provided for discussion purposes only. Intel will have no liability to make any purchase in connection with forecasts published in this document. Intel accepts no duty to update this presentation based on more current information. Intel is not liable for any damages, direct or indirect, consequential or otherwise, that may arise, directly or indirectly, from the use or misuse of the information in this presentation. Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

Copyright © 2018 Intel Corporation.

Intel, the Intel logo, Xeon. Movidius and Stratix are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others