| |

CHAPI

Calcul embarqué Hautes performances

pour les Applications Industrielles,

petites & moyennes séries

Porteur :

Appel à projet :

Statut :

Groupes Thématiques de SYSTEMATIC :

Date de début du projet :

Date de fin de projet :

Durée :

Montant total :

Montant aide :

Partenaires du projet :

Pour télécharger la fiche du projet,

Le projet CHAPI adresse la problématique du calcul embarqué hautes performances ; Il vise à accompagner l’émergence d’une nouvelle génération de circuits programmables hautes performances, massivement parallèles, pour les applications industrielles, petites et moyennes séries.

Les technologies étudiées dans le projet visent spécifiquement les marchés des systèmes embarqués, et permettront de palier les freins et contraintes rencontrés par les concepteurs de systèmes intégrant des composants FPGA, ASIC ou DSP qui atteignent leurs limites de performances, de coût et de flexibilité de développement.

-

Les coûts et surtout les temps de développement des solutions basées sur des ASIC ou des FPGA deviennent de moins en moins compatibles avec les besoins & la complexité croissante des systèmes, ainsi que le raccourcissement des cycles de vie des produits

-

Les performances des microcontrôleurs et DSP pour les systèmes embarqués sont limitées par leurs architectures classiques ou spécialisées, ainsi que par les contraintes fortes en terme de consommation.

-

Par la même tendance que pour les processeurs généralistes, des microcontrôleurs multi-cœur commencent à apparaître (2, 4) mais ils sont soit spécialisés (chaque coeur remplit un rôle particulier et est optimisé pour cela), soit globalement limités en performance et en montée en charge

L’émergence de solutions massivement parallèles pour les applications embarquées se confirme depuis quelques années au travers d’initiatives de R&D en Europe et aux Etats-Unis ainsi que par la création de plusieurs sociétés visant à fournir ce type de solutions.

La société Kalray, créée en Juillet 2008, développe la solution MPPA™ (Multi-Purpose Processor Array), nouvelle génération de processeurs massivement parallèles pour les applications industrielles, technologie qui est au cœur du projet CHAPI.

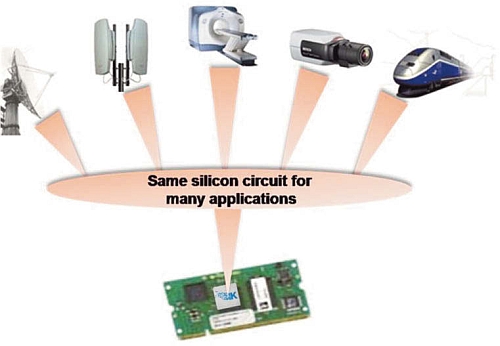

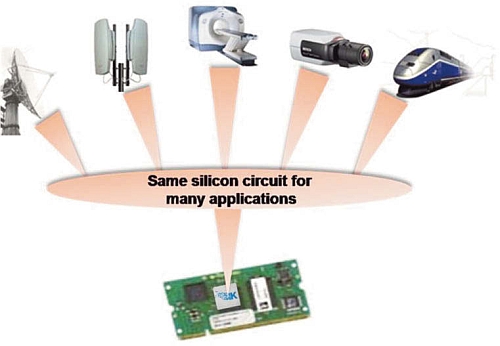

La généricité de ces solutions, c'est-à-dire leur capacité à supporter des applications et des domaines multiples, est une caractéristique essentielle de l’approche ; MPPA™ vise à supporter des applications des domaines du Multimédia (traitement d’image, codage) des Telecom (flux de données, traitement de signal) mais aussi plus généralement des applications mêlant des traitements intensifs à des besoins de contrôle importants.

est d’accompagner et d’amplifier la mise en œuvre opérationnelle de cette solution en rupture issue de différents travaux du pôle et de ses acteurs, sur différents aspects clés : est d’accompagner et d’amplifier la mise en œuvre opérationnelle de cette solution en rupture issue de différents travaux du pôle et de ses acteurs, sur différents aspects clés :

|